## Sixth Semester B.E. Degree Examination, Dec.2019/Jan.2020 **VLSI** Design

Time: 3 hrs.

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Module-1

Explain the step-by-step CMOS P-Well fabrication process. 1 a.

(08 Marks)

With the mathematical equations, explain velocity saturation and mobility degradation effect b. due to increase in saturation current. (08 Marks)

OR

With the transfer characteristic of skewed inverter, explain the beta ratio effects. (06 Marks) 2 a.

Compare CMOS and bipolar technologies. b.

(06 Marks)

c. Consider the nMOS transistor in a 180 nm process with a nominal threshold of 0.4V and doping level of  $8 \times 10^{17}$  cm<sup>-3</sup>. The body is tied to ground with a substrate contact. How much does the threshold change at room temperature if the source is at 1.1V instead of '0'?

(04 Marks)

Module-2

Discuss the λ-based design rules (i) Butting contact (ii) Transistors (nMOS, pMOS and 3 CMOS) (08 Marks)

Derive the expression of delay in terms of  $\tau$  for CMOS inverter pair.

(08 Marks)

4 Draw the layout for Y = A + BC using CMOS.

(08 Marks)

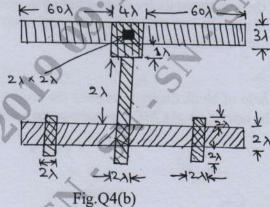

Find the C<sub>in</sub> for the layout shown in Fig. Q4(b).

(08 Marks)

Module-3

Define scaling. Explain the scaling factors for device parameters. 5

(08 Marks)

What is Manchester Carry Chain? Explain it.

(08 Marks)

OR

What are the problems associated with VLSI design and how to reduce by using standard (06 Marks) practice?

Draw the  $4 \times 4$  cross bar switch using MOS switches and explain it.

(06 Marks)

Calculate the Regularity for  $4 \times 4$  bit and  $8 \times 8$  bit shifter.

(04 Marks)

Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages. 2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be

Module-4

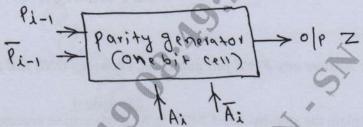

7 a. Construct a stick diagram for an nMOS parity generator as shown in Fig.Q7(a). The required response is such that z = 1 if there is an even number (including zero) of 1s on the input and z = 0 if there is an odd number.

Fig.Q7(a)

(08 Marks)

b. Draw the block diagram of Generic structure of an FPGA fabric and explain it. (08 Marks)

OR

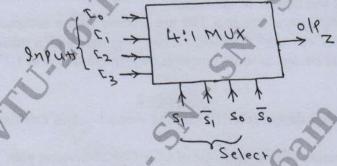

8 a. Construct a stick diagram for an multiplexer shown in Fig.Q8(a) using CMOS.

Fig.Q8(a)

(08 Marks)

b. Explain the goals and techniques of FPGA based system design.

(08 Marks)

Module-5

- 9 a. What are the requirements for system timing considerations? (06 Marks)

b. Explain the operation of a three transistor dynamic RAM cell. (06 Marks)

- c. Write a note on stuck at faults.

(04 Marks)

OR

- 10 a. With the help of block diagram, explain the process of logic verification. (08 Marks)

- b. Explain the operation of CMOS pseudo-static memory cell.

(08 Marks)